纠错

全专业资料、题库、学位、网课

最高直省2344元

上千+科次精品网课

买网课即送全真模考题库

五千+科次教材资料

电子资料满三件9折

五千+科次在线题库

全真呈现历年考试试题

1、[主观题]【简答题】简述硬件描述语言HDL(VHDL/VerilogHD软件)开发PLD/FPGA的完整流程。

2、[主观题]【程序分析题】分析下面的Verilog HDL程序,回答问题。

module test1 (inI, in2, in3, in4, sel,_____);

input [1: 0] in1, in2, in3. in4

input [1: 0] sel;

output [1: 0] data_ out

____[1: 0] data_ out;

always @(in1 or in2 or in3 or in4 or sel)

case(sel)

2'b00: data_out <=in1

2'b01: data_ out < in2

2'1b10: data_ out < in3

2'b11: data_ out <= in4

default: data_ out < in1;

______

endmodule

(1)完成程序填空

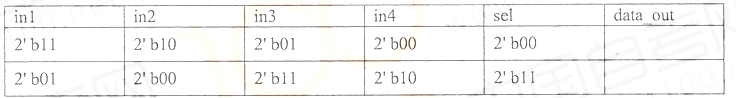

(2)分析该模块的功能,根据输入信号得到相应的输出信号,完成题表。

3、[主观题]【简答题】简述什么是电子设计自动化技术?它的发展分为哪二三个阶段?

4、[主观题]【编程题】已知一有限状态机系统的状态转移如题图所示,试用VerilogHDL设计该系统。

说明

(1)该电路系统有三种状态:S1,S2,S3

(2)系统具有同步复位功能

(3)系统输入信号是

clk:系统时钟

in:1bit位宽的输入数据

rst:1bit位宽的同步复位信号,当rst=1时系统状态复位为S1。

当rst=0时,系统按照题图所示的状态转移图工作

(4)系统输出信号是:

out:1bit位宽的输出数据

(5)状态转移图的图示说明:1/0表示,当输入in=1'b1时,相应输出out=1'b0,以此类推。

5、[主观题]【简答题】简述Multisim电路仿真过程的主要步骤。

Copyright © 2010 - 2023 湖南求实创新教育科技有限公司 All Right Reserved.

温馨提示:如您需要的资料本网暂时没有,请于工作日08:00-18:00,点击这里,联系客服及时补充资料。